FPGA之IO信号类型深入理解

本文共 3408 字,大约阅读时间需要 11 分钟。

在FPGA设计开发中,很多场合会遇到同一根信号既可以是输入信号,又可以是输出信号,即IO类型(Verilog定义成inout)。

对于inout型的信号,我们既可以使用FPGA原语来实现,也可以使用Verilog代码来实现。下面将介绍在Xilinx 7系列FPGA上两种实现方式的差别和注意点。

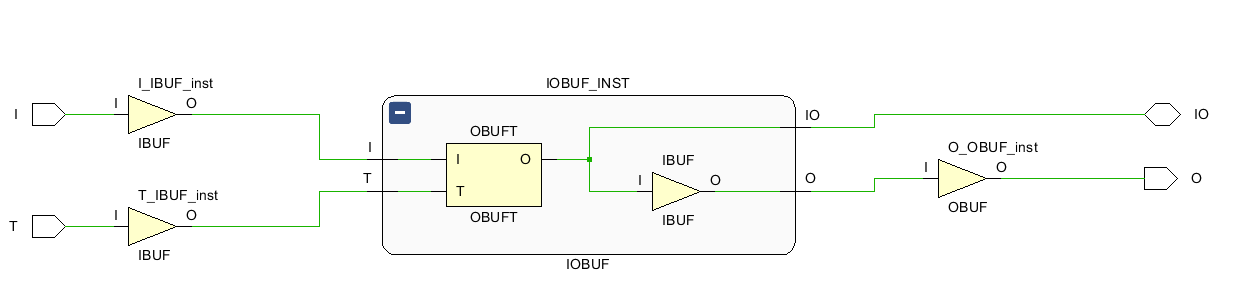

不管哪种方式实现IO功能,从编译结果看都会调用IOBUF原语,为此,我们先来看一下IOBUF的结构,如下图所示。

1.FPGA原语实现

首先,我们编写的代码如下:

1`define PRIMITIVE 2 3 module io_buf( 4 input T , 5 input I , 6 output O , 7 inout IO 8 ); 9 10 `ifdef PRIMITIVE11 IOBUF #(12 .DRIVE (12 ), // Specify the output drive strength13 .IBUF_LOW_PWR ("TRUE" ), // Low Power - "TRUE", High Performance = "FALSE" 14 .IOSTANDARD ("DEFAULT" ), // Specify the I/O standard15 .SLEW ("SLOW" ) // Specify the output slew rate16 ) IOBUF_INST (17 .O (O ), // Buffer output18 .IO (IO ), // Buffer inout port (connect directly to top-level port)19 .I (I ), // Buffer input20 .T (T ) // 3-state enable input, high=input, low=output21 );22 `else23 assign IO = T? I:1'bz;24 assign O = IO;25 `endif26 27 endmodule 该代码通过原语IOBUF实现IO功能,使用Vivado编译后的原理图如下图所示。可以看到IOBUF内部由OBUFT和IBUF原语构成。

2.使用Verilog实现

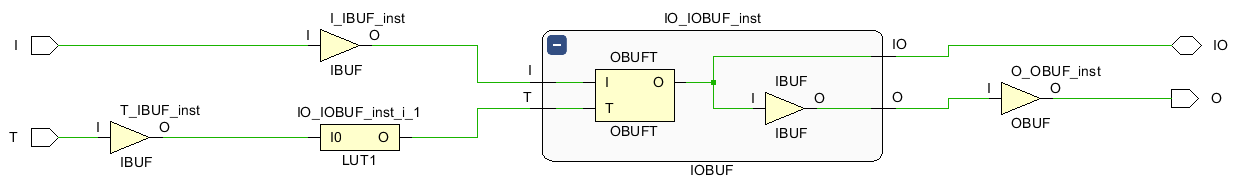

把`define PRIMITIVE注释掉,则为通过Verilog的实现方式,如下图:

//`define PRIMITIVE module io_iobuf( input T , input I , output O , inout IO);`ifdef PRIMITIVE IOBUF #( .DRIVE (12 ), // Specify the output drive strength .IBUF_LOW_PWR ("TRUE" ), // Low Power - "TRUE", High Performance = "FALSE" .IOSTANDARD ("DEFAULT" ), // Specify the I/O standard .SLEW ("SLOW" ) // Specify the output slew rate ) IOBUF_INST ( .O (O ), // Buffer output .IO (IO ), // Buffer inout port (connect directly to top-level port) .I (I ), // Buffer input .T (T ) // 3-state enable input, high=input, low=output );`else assign IO = T? I:1'bz; assign O = IO;`endif endmodule 该代码使用Vivado编译后的原理图如下图所示。该实现方式也会调用IOBUF原语,但多消耗了一个LUT资源。

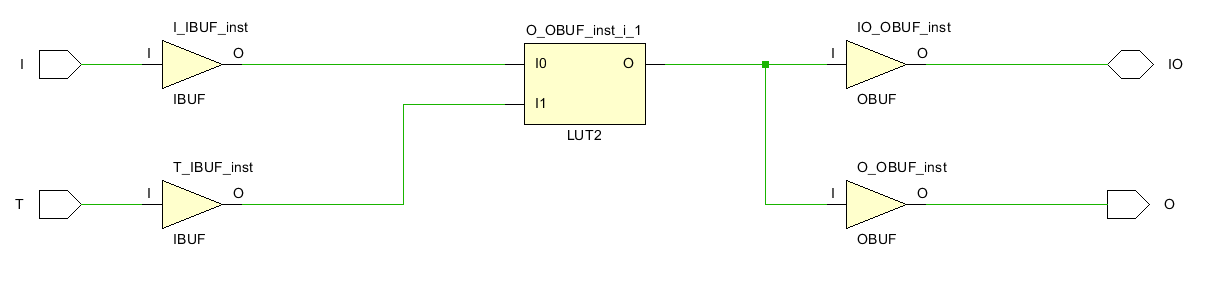

通过Verilog实现时,我们在把IO信号当成输入时给赋值高阻态(1‘bz)。假如我们把此时的IO信号赋值1‘b0或者1‘b1,会出现什么情况呢?我们把1‘bz写成1‘b1,如下所示:

1 //`define PRIMITIVE 2 3 module io_iobuf( 4 input T , 5 input I , 6 output O , 7 inout IO 8 ); 9 10 `ifdef PRIMITIVE11 IOBUF #(12 .DRIVE (12 ), // Specify the output drive strength13 .IBUF_LOW_PWR ("TRUE" ), // Low Power - "TRUE", High Performance = "FALSE" 14 .IOSTANDARD ("DEFAULT" ), // Specify the I/O standard15 .SLEW ("SLOW" ) // Specify the output slew rate16 ) IOBUF_INST (17 .O (O ), // Buffer output18 .IO (IO ), // Buffer inout port (connect directly to top-level port)19 .I (I ), // Buffer input20 .T (T ) // 3-state enable input, high=input, low=output21 );22 `else23 assign IO = T? I:1'b1;24 assign O = IO;25 `endif26 27 endmodule 编译后的原理图如下,可以看到并不会调用IOBUF原语,IO的不能实现输入功能,这就是解释了为什么在使用Verilog实现一根信号的IO功能时需要赋值1‘bz。

转载地址:http://jmxii.baihongyu.com/

你可能感兴趣的文章

用STL algorithm轻松解决几道算法面试题

查看>>

ACfly之所以不怕炸机因为它觉得某个传感器数据不安全就立马不用了

查看>>

我发觉,不管是弄ROS OPENCV T265二次开发 SDK开发 caffe PX4 都是用的C++

查看>>

ROS的安装(包含文字和视频教程,我的ROS安装教程以这篇为准)

查看>>

原来我之前一直用的APM固件....现在很多东西明白了。

查看>>

realsense-ros里里程计相关代码

查看>>

似乎写个ROS功能包并不难,你会订阅话题发布话题,加点逻辑处理,就可以写一些基础的ROS功能包了。

查看>>

PX4官方用户和开发手册的首页面是会给你选择英文和中文的

查看>>

博士的申请考核制

查看>>

找到了中文版的mavlink手册

查看>>

浅谈飞控开发的仿真功能

查看>>

我觉得在室内弄无人机开发装个防撞机架还是很有必要的,TBUS就做得很好。

查看>>

serial也是见到很多次了,似乎它就是一种串行通信协议

查看>>

TBUS的一些信息

查看>>

专业和业余的区别就在于你在基础在基本功打磨练习花的时间

查看>>

通过mavlink实现自主航线的过程笔记

查看>>

Ardupilot飞控Mavlink代码学习

查看>>

这些网站有一些嵌入式面试题合集

查看>>

我觉得刷题是有必要的,不然小心实际被问的时候懵逼,我觉得你需要刷个50份面试题。跟考研数学疯狂刷卷子一样!

查看>>

我觉得嵌入式面试三要素:基础吃透+项目+大量刷题,缺一不可。不刷题是不行的。而且得是大量刷,刷出感觉套路,别人做题都做得是固定题型套路条件反射了,你还在那慢慢理解慢慢推是不行的,也是考研的教训。

查看>>